速報

明らかになったCellの詳細

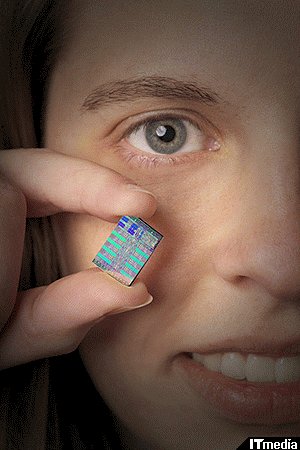

64ビットPOWERと8個のSynergistic Processing Units(SPU)で構成し、初期テストで4GHz超、2.5Mバイトオンチップメモリ。マルチOSの同時実行など。

advertisement

米IBM、ソニー・コンピュータエンタテインメント、東芝が2月8日に明らかにした「Cell」プロセッサの詳細は以下の通り。

・概要

- 高性能な浮動小数点演算機能を持つ8個のSynergistic Processing Units(SPU)と64ビットPOWERベースコア。初期テストで4GHz超

- マルチOSの同時実行

- 独自回路技術、設計再利用のためのモジュール性とカスタムクロック構造、独自のパワー・熱制御コンセプトのデザインへの採用

・マルチコアアーキテクチャ

- 各128本の128ビットレジスタファイルと256Kバイトのローカルストアを持つ独立した8個のSPU

- 2スレッドSMT機能を持つVMX拡張付き64ビットPower Architecture。システムメモリに対し10ウェイのコヒーレントスレッドマシンとして認識

- 2.5Mバイトオンチップメモリ(512KバイトL2キャッシュ+8×256Kバイト)

- 試作チップ面積は221平方ミリ

- 90ナノメートルSOI(Silicon-On-Insulator)

- モジュラー構造を採用し、SPU数の増減で浮動小数点演算能力を調整可能

・ブロードバンドアーキテクチャ

- 64ビットPower Arichitectureとの互換性

- SPUはSIMD構造とローカルストアを持つRISCアーキテクチャ

- プロセッサ当たり128以上のメモリへの同時データトランザクション

- 96バイト/サイクルのハイスピード内部インターコネクトバス

・リアルタイムアーキテクチャ

- リソース割付機能(帯域幅制御のため)

- キャッシュロック機能(置換制御テーブルによる)

- 同時実行される複数OSにまたがるリアルタイム応答性を持つ仮想化機能サポート

・その他

- 柔軟なセキュリティプログラムを実現するSPUダイナミックコンフィギュレーション

- 従来型アプリケーションとリアルタイムアプリケーションをサポートする仮想化技術

- 自律的パワー制御機能

- リアルタイムヒューマンインタラクションを実現するリソースマネジメント

- 帯域幅を持続する高性能なメモリーフローコントローラ(DMA)

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

- “Cell”プロセッサの概要明らかに――マルチコアで4GHz超え

IBM、SCE、東芝の3社はISSCCで共同開発中のマイクロプロセッサCellの概要を初めて明らかにした。 - Cellプロセッサの仕様が明らかに――動作速度は4GHz超に

ソニー、IBM、東芝はISSCCでPS3に搭載する「Cell」チップの技術仕様について発表した。 - [WSJ] ソニーら、ISSCCで「Cell」の設計披露へ

Cellの概要は既に公表されているが、7日に開かれる国際固体素子回路会議(ISSCC)では、同プロセッサの基本設計が初めて明らかにされる見込みだ。